## **GS66508B-EVBDB1**

# GaN E-HEMT Daughter Board and GS665MB-EVB Evaluation Platform

**Technical Manual**

Visit www.gansystems.com for the latest version of this technical manual.

#### **DANGER!**

This evaluation kit is designed for engineering evaluation in a controlled lab environment and **should be handled by qualified personnel ONLY**. High voltage will be exposed on the board during the test and even brief contact during operation may result in severe injury or death.

Never leave the board operating unattended. After it is de-energized, always wait until all capacitors are discharged before touching the board.

#### CAUTION

This product contains parts that are susceptible to damage by electrostatic discharge (ESD). Always follow ESD prevention procedures when handling the product.

## GS66508B-EVBDB1

## 650V GaN E-HEMT Evaluation Board Technical Manual

## **Overview**

The GS66508B-EVBDB1 daughter board style evaluation kit consists of two GaN Systems 650V GaN Enhancement-mode HEMTs (E-HEMTs) and all necessary circuits including half bridge gate drivers, isolated power supplies and optional heatsink to form a functional half bridge power stage. It allows users to easily evaluate the GaN E-HEMT performance in any half bridge-based topology, either with the universal mother board (P/N: GS665MB-EVB) or for quick prototyping of a users' own system design.

#### **Features**

- Serves as a reference design and evaluation tool as well as deployment-ready solution for easy insystem evaluation.

- Vertical mount style with height of 35mm, which fits in majority of 1U design and allows evaluation of GaN E-HEMT in traditional through-hole type power supply board.

- Current shunt position for switching characterization testing

- Universal form factor and footprint for all products

The daughter board and universal mother board ordering part numbers are below:

### Table 1 Ordering part numbers

| Part Number     | GaN E-HEMT | Description                                            |

|-----------------|------------|--------------------------------------------------------|

|                 | P/N:       |                                                        |

| GS66508B-EVBDB1 | GS66508B   | GaN E-HEMT bottom side cooled $650V/30A$ , $50m\Omega$ |

|                 |            | Analog Devices isolated driver ADUM4121ARZ             |

| GS665MB-EVB     |            | Universal 650V Mother Board                            |

#### Control and Power I/Os

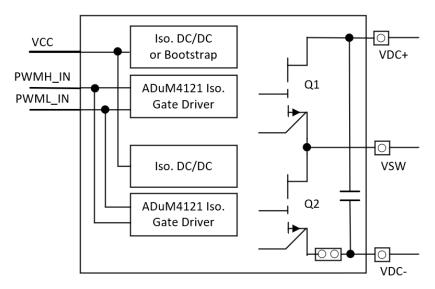

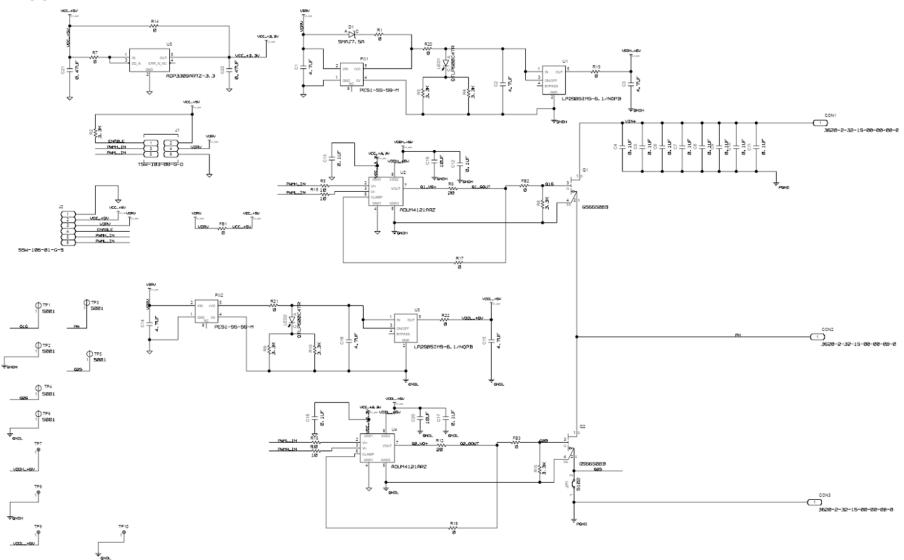

The daughter board GS6650B8-EVBDB1 circuit diagram is shown in Figure 1. The control logic inputs on 2x3 pin header J1 are listed below:

## Table 2 Control pins

| Pin  | Descriptipon                                                                            |

|------|-----------------------------------------------------------------------------------------|

| ENA  | Enable input. It is internally pulled up to VCC, a low logic disables all the PWM gate  |

|      | drive outputs.                                                                          |

| VCC  | +5V auxillary power supply input for logic circuit and gate driver. On the daughter     |

|      | board there are 2 isolated 5V to 9V DC/DC power supplies for top and bottom switches.   |

| VDRV | Optional 9V gate drive power input. This pin allows users to supply separate gate drive |

|      | power supply. By default VDRV is connected to VCC on the daughter board via a 0 ohm     |

|      | jumper FB1. If bootstrap mode is used for high side gate drive, connect VDRV to 9V      |

| PWMH | High side PWM logic input for top switch Q1. It is compatible wth 3.3V and 5V           |

| PWML | Low side PWM logic input for bottom switch Q2. It is compatible wth 3.3V and 5V         |

| 0V   | Logic inputs and gate drive power supply ground return.                                 |

## **Power pins**

The 3 power pins are

- VDC+: Input DC Bus voltage

- VSW: Switching node output

- VDC-: Input DC bus voltage ground return. Note that control ground 0V is isolated from VDC-.

Figure 1 - GS66508B-EVBDB1 Evaluation Board Block Diagram

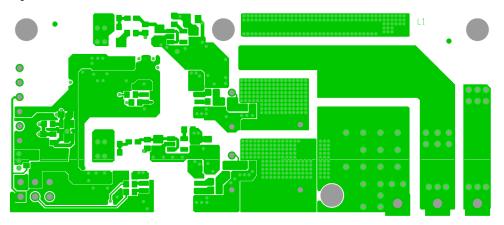

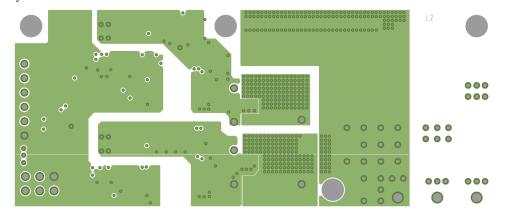

## GS66508B-EVBDB1 half bridge daughter board

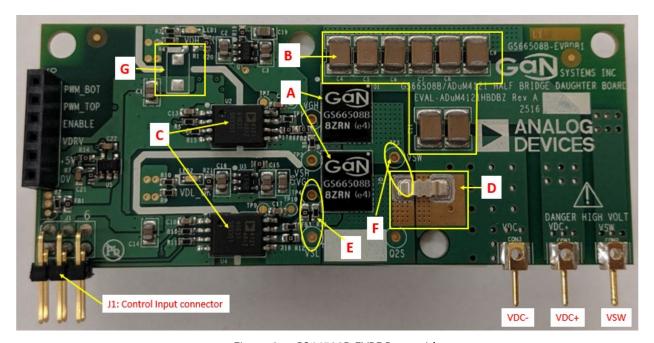

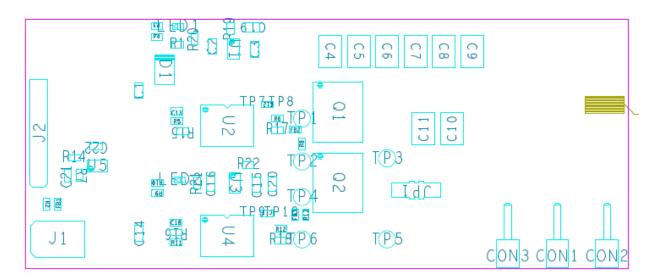

Figure 2 - GS66508B-EVBDB top side

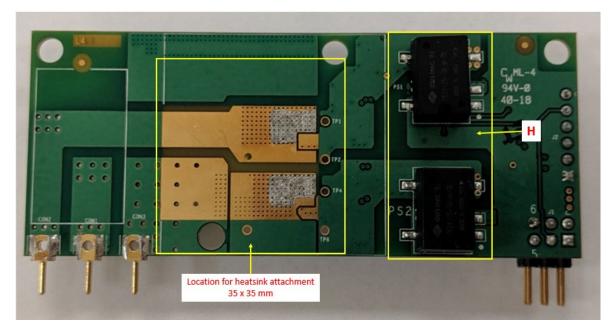

Figure 3 - GS66508B-EVBDB bottom side

- A. 2x GaN Systems 650V E-HEMT GS66508B,  $30A/50m\Omega$

- B. Decoupling capacitors C4-C11

- C. 2 x Analog Devices ADuM4121ARZ Isolated gate driver

- D. Optional current shunt position JP1.

- E. Test points for bottom Q2 V<sub>GS</sub>.

- F. Recommended probing positions for Q2 VDs.

- G. Optional bootstrap circuit D1/R1 (unpopulated).

- H. 5V-9V isolated DC/DC gate drive power supply

### **GaN E-HEMTs**

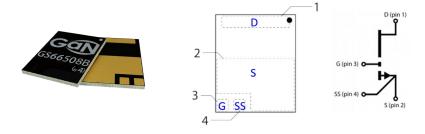

This daughter board includes two GaN Systems GS66508B (650V/30A,  $50m\Omega$ ) E-HEMTs in a GaN*PX*® bottom cooled package. The large S pad serves as the Source connection and thermal pad. Pin 4 is the Kelvin source connection for the gate drive return.

Figure 4 - Package outline of GS66508B

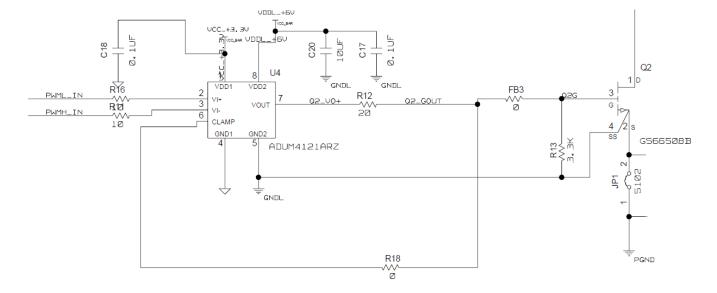

#### **Gate driver circuit**

• The half bridge evalualtion boards use two Analog Devices high voltage, isolated gate drivers (ADuM4121ARZ) to drive the GaN transistors directly. The ADuM4121ARZ gate driver is used to isolate and drive the GaN transistor, operating at high DC bus voltage. It has a rail-to-rail output with maximum output current of 2A to turn the GaN device on and off efficiently and reliably. An external  $20\Omega$  gate resistor is used to limit the current for sourcing and sinking.

- The ADuM4121ARZ has a propagation delay of less than 53 ns and typical rise and fall times of approximately 18 ns. The very high Common-mode transient immunity (CMTI) of 150 kV/us (min) isolates high transient noise during the high frequency operation and prevents erroneous outputs.

- The GaN E-HEMT switching speed and slew rate can be directly controlled by the gate resistors. By default the turn-on/turn-off gate resistors, R6/R12, are  $20\Omega$ . The user can adjust the values of gate resistors to fine tune the turn-on and turn-off speed.

- FB2/FB3 are footprints for optional ferrite bead. By default they are populated with  $0\Omega$  jumpers. If gate oscillation is observed, it is recommended to replace them with ferrite bead with Z=10- $20\Omega$ @100MHz.

Figure 5 - Gate driver circuit

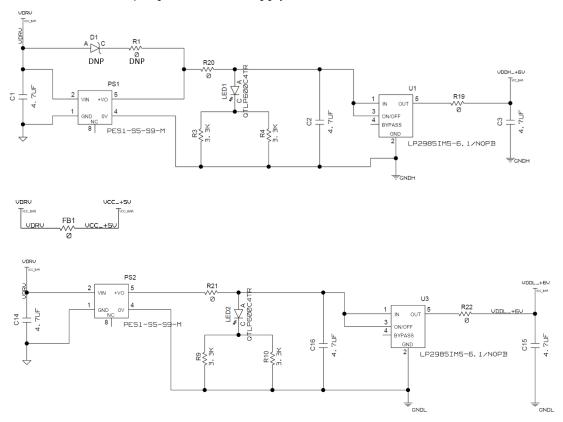

## Gate drive power supply

- 5V-9V isolated DC/DC converters are used for the gate drive. The 9V output is regulated down to 6V for the gate driver.

- By default gate drive supply input VDRV is tied to VCC +5V via  $0\Omega$  jumper (FB1). Remove FB1 if separate gate drive input voltage is to be used.

#### **Bootstrap** mode

• The board has the option for users to experiment with non-isolated bootstrap circuit with following circuit changes:

- - Remove PS2 and short circuit pin 2 to 5 and pin 1 to 4.

- o Populate D1/R1 (not supplied): D1 is the high voltage bootstrap diode (for example ES1J) and use 1-2 $\Omega$  0805 SMD resistor on R1. Depopulate PS1, LED1 and replace C2 with 1uF capacitor.

- o Remove  $0\Omega$  jumper at FB1 and supply +9V at VDRV.

Figure 6 - Gate drive power supply with optional bootstrap mode

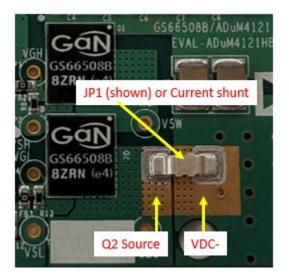

### **Current shunt JP1**

- The board provides an optional current shunt position JP1 between the source of Q2 and power ground return. This allows drain current measurement for switching characterization test such as Eon/Eoff measurement.

- The JP1 footprint is compatible with T&M Research SDN series coaxial current shunt (recommended P/N: SDN-414-10, 2GHz B/W,  $0.1\Omega$ )

- If current shunt is not used JP1 must be shorted. JP1 affects the power loop inductance and its inductance should be kept as low as possible. Use a copper foil or jumper with low inductance.

#### **CAUTION**

Check the JP1 before the first time use. To complete the circuit JP1 needs to be either shorted or a current shunt must be inserted before powering up.

Figure 7 - Current shunt position JP1

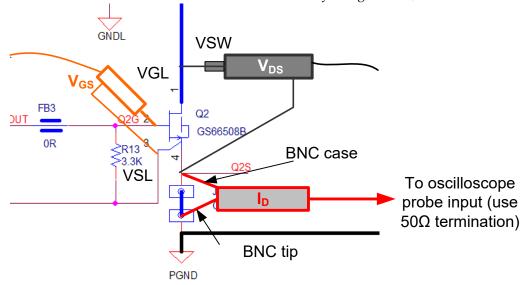

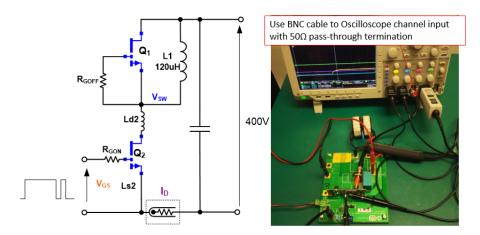

## Measurement with current shunt

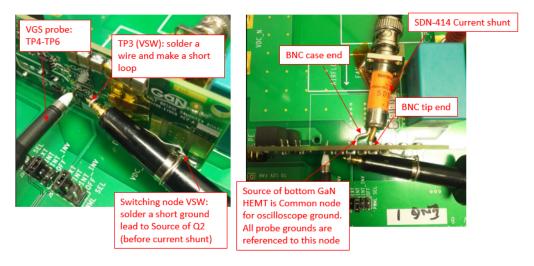

- 1. When measuring VSW with current shunt, ensure all channel probe grounds and current shunt BNC output case are all referenced to the source end of Q2 before the current shunt. The recommended setup of probes is shown as below.

- 2. The output of coaxial current shunt can be connected to oscilloscope via  $50\Omega$  termination impedance to reduce the ringing.

- 3. The measured current is inverted and can be scaled by using: Id=Vid/Rsense.

Figure 8 - Recommended probe connection with current shunt

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

## Thermal design

- 1. GS66508B has a thermal pad at the bottom side for heat dissipation. The heat is transferred to the bottom side of PCB using thermal vias and copper plane.

- 2. A heatsink (35x35mm size) can be attached to the bottom side of board for optimum cooling. Thermal Interface Material (TIM) is needed to provide electrical insulation and conformance to the PCB surface. The daughter board evaluation kit includes a sample 35x35mm fin heatsink (not installed), although other heatsinks can also be used to fit users' system design.

- 3. A thermal tape type TIM (Berguist® Bond-Ply 100) is chosen for its easy assembly. The supplied heatsink has the thermal tape pre-applied so simply peel off the protective film and attach the heatsink to the back of board as marked in Figure 3.

- 4. Two optional mounting holes as shown in Figure 9 are provided for mounting customized heatsink using screws.

- 5. Using the supplied heatsink and TIM, the overall junction to ambient thermal resistance  $R_{thJ-A}$  is  $\sim 9^{\circ}C/W$  with 500LFM airflow.

- 6. Forced air cooling is recommended for power testing.

Figure 9 The daughter board with heatsink attached

#### **CAUTION:**

There is no on-board over-temperature protection. Device temperature must be closely monitored during the test. Never operate the board with device temperature exceeding  $T_{J\_MAX}$  (150°C)

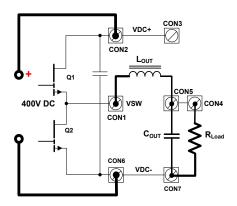

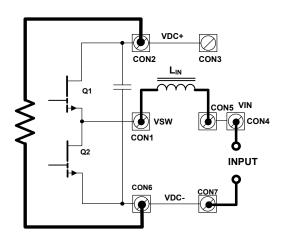

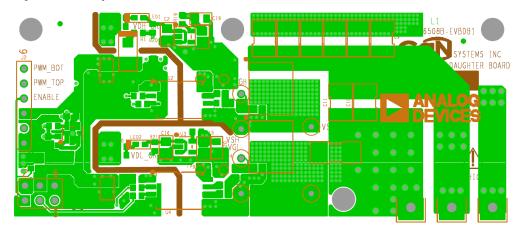

# Using GS66508B-EVBDB1 with universal mother board GS665MB-EVB

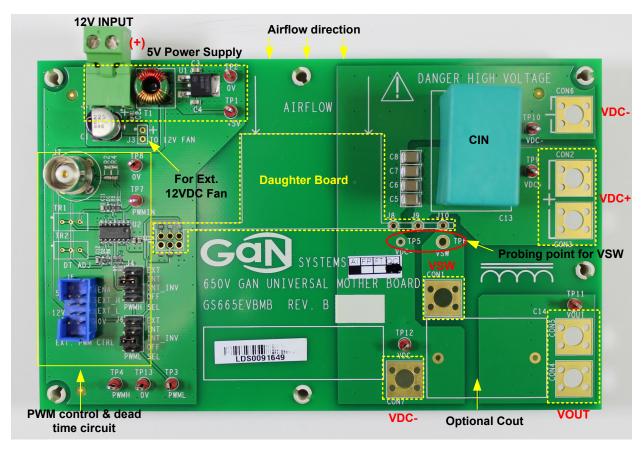

Figure 10 - 650V universal mother board GS665MB-EVB

GaN Systems offers a universal 650V mother board (ordering part number: GS665MB-EVB, sold separately) that can be used as the basic evaluation platform for all the daughter boards.

The universal 650V mother board evaluation kit includes following items:

- 1. Mother board GS665MB-EVB

- 2. 12VDC Fan

### 12V input

The board can be powered by 9-12V on J1. On-board voltage regulator creates to 5V for daughter board and control logic circuits. J3 is used for external 12VDC fan.

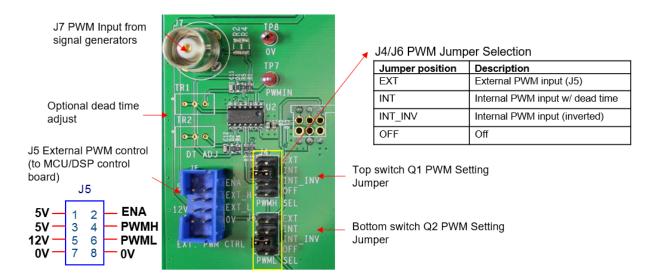

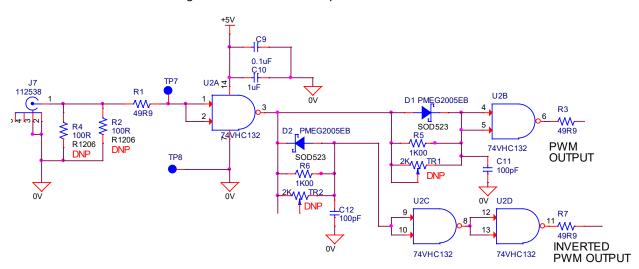

#### **PWM control circuit**

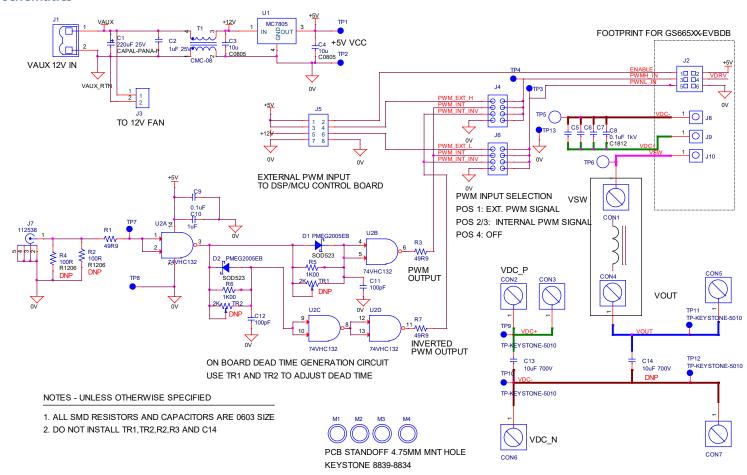

Figure 11 - PWM control input and dead time circuit

Figure 12 - On board dead time generatrion circuit

The top and bottom switches PWM inputs can be individually controlled by two jumpers J4 and J6. Users can choose between a pair of complementary on-board internal PWM signals (non-inverted and inverted, controlled by J7 input) with dead time or external high/low side drive signals from J5 (users' own control board).

An on-board dead time generation circuit is included on the mother board. Dead time is controlled by two RC delay circuits, R6/C12 and R5/C11. The default dead time is set to about 100ns. Additionally two potentiometers locations are provided (TR1/TR2, not included) to allow fine adjustment of the dead time if needed.

## GS66508B-EVBDB1

## 650V GaN E-HEMT Evaluation Board Technical Manual

# $\wedge$

#### WARNING

<u>ALWAYS</u> double check the jumper setting and PWM gate drive signals before applying power. Incorrect PWM inputs or jumper settings may cause device failures

### **Test points**

Test points are designed in groups/pairs to facilitate probing:

| Test points  | Name         | Description                                               |

|--------------|--------------|-----------------------------------------------------------|

| TP1/TP2      | +5V/0V       | 5V bias power                                             |

| TP7/TP8      | PWMIN/0V     | PWM input signal from J7                                  |

| TP4/TP3/TP13 | PWMH/PWML/0V | High/low side gate signals to daughter board              |

| TP9/TP10     | VDC+/VDC-    | DC bus voltage                                            |

| TP11/TP12    | VOUT/VDC-    | Output voltage                                            |

| TP6/TP5      | VSW/VDC-     | Switching node output voltage (for HV oscilloscope probe) |

#### **Power connections**

CON1-CON7 mounting pads are designed to be compatible with following mounting terminals:

- #10-32 Screw mount,

- Banana Jack PCB mount (Keystone P/N: 575-4), or

- PC Mount Screw Terminal (Keystone P/N: 8191)

## **Output passives (L and C14)**

An external power inductor (not included) can be connected between VSW (CON1) and VOUT (CON4/5) or VDC+ (CON2/3) for double pulse test. Users can choose their inductor size to meet the test requirement. Generally it is recommended to use power inductor with low inter-winding capacitance to obtain best switching performance. For the double pulse testing we use 2x 60uH/40Amp inductor (CWS, P/N: HF467-600M-40AV) in series. C14 is designed to accommodate a film capacitor as output filter.

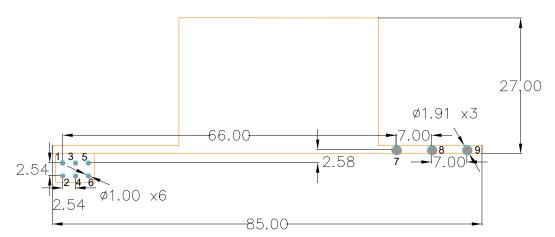

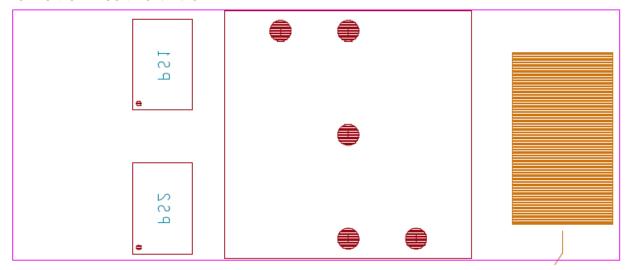

## Using GS66508B-EVBDB1 in system

The daughter board allows users to easily evaluate the GaN performance in their own systems. Refer to the footprint drawing of GS66508B-EVBDB1 shown in figure 14.

- 1. All units are in mm.

- 2. Pin 1-6: Dia. 1mm

- 3. Pin 7-9: 1.91mm (75mil) mounting hole for Mill-max Receptacle P/N: 0312-0-15-15-34-27-10-0.

Figure 13 - Recommended footprint drawing of daughter board GS66508B-EVBDB1

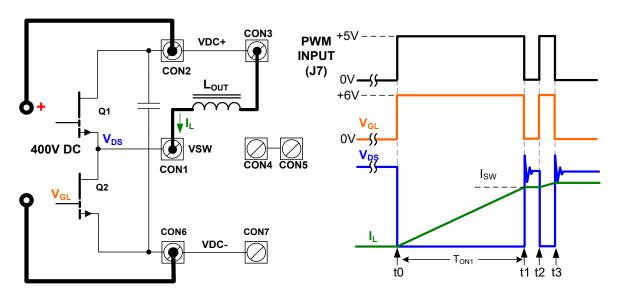

## Double pulse test mode

Figure 14 - Double pulse test setup

Double pulse test allows easy evaluation of device switching performance at high voltage/current without the need of actually running at high power. It can also be used for switching loss (Eon/Eoff) measurement and other switching characterization parameter test.

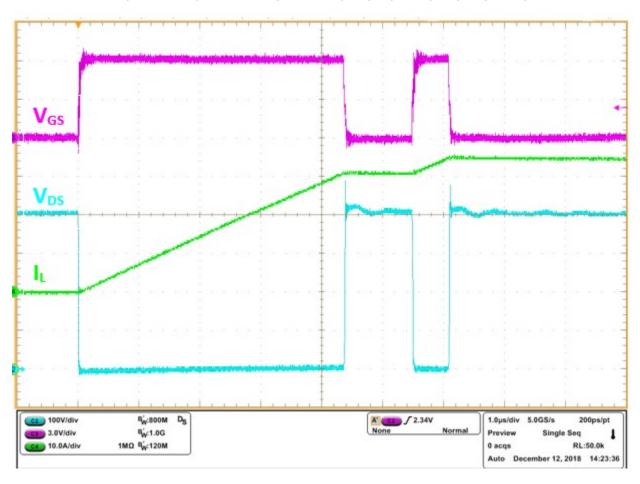

The circuit configuration and operating principle can be found in Figure 13:

- 1. The output inductor is connected to the VDC+.

- 2. At t0 when Q2 is switched on, the inductor current starts to ramp up until t1. The period of first pulse Ton1 defines the switching current  $I_{SW} = (V_{DS}*T_{ON1}) / L$ .

- 3. t1-t2 is the free wheeling period when the inductor current IL forces Q1 to conduct in reverse.

- 4. t1 (turn-off) and t2 (turn-on) are of interest for this test as they are the hard switching trasients for the half bridge circuit when Q2 is under high switching stress.

- 5. The second pulse t2-t3 is kept short to limit the peak inductor current at t3.

The double pulse signal can be generated using programmable signal generator or microcontroller/DSP board. As this test involves high switching stress and high current, it is recommended to set the double pulse test gate signal as single trigger mode or use long repetition period (for example >50-100ms) to void excess stress to the switches. Q1 can be kept off during the test or driven synchronously (J4 set to OFF or INT\_INV) and Q2 is set to INT (or EXT position if PWM signal is from J5).

#### WARNING

Limit the maximum switching test current to 30A and ensure maximum drain voltage, including ringing, is kept below 650V for pulse testing. Exceeding this limit may cause damage to the devices.

## **Buck/Standard half bridge mode**

This is standard half bridge configuration that can be used in following circuits:

- Synchronous Buck DC/DC

- Single phase half bridge inverter

- ZVS half bridge LLC

- Phase leg for full bridge DC/DC or

- Phase leg for a 3-phase motor drive

## Jumper setting:

- J4 (Q1): INT

- J6 (Q2): INT\_INV

## **Boost mode**

When the output becomes the input and the load is attached between VDC+ and VDC-, the board is converted into a boost mode circuit and can be used for:

- Synchronous Boost DC/DC

- Totem pole bridgeless PFC

## Jumper setting:

- J4 (Q1): INT\_INV

- J6 (Q2): INT

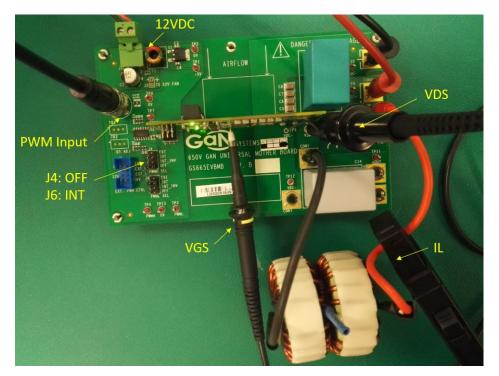

## **Quick Start procedure – Double pulse test**

Follow the instructions below to quickly get started with your evaluation of GaN E-HEMT. Equipment and components you will need:

- Four-channel oscilloscope with 500MHz bandwidth or higher

- high bandwidth (500MHz or higher) passive probe

- high bandwidth (500MHz) high voltage probe (>600V)

- AC/DC current probe for inductor current measurement

- 12V DC power supply

- Signal generator capable of creating testing pulses

- High voltage power supply (0-400VDC) with current limit.

- External power inductor (recommend toroid inductor 50-200uH)

- 1. Check the JP1 on daughter board GS66508B-EVBDB1. Use a copper foil and solder to short JP1.

- 2. Install GS66508B-EVBDB1 on the mother board. Press all the way down until you feel a click. Connect probe between VGL and VSL for gate voltage measurement.

- 3. Set up the mother board:

- a. Connect 12VDC bias supply to J1.

- b. Connect PWM input gate signal (0-5V) to J7. If it is generated from a signal generator ensure the output mode is high-Z mode.

- c. Set J4 to OFF position and J7 to INT.

- d. Set High voltage (HV) DC supply voltage to 0V and ensure the output is OFF. Connect HV supply to CON2 and CON6.

- e. Use HV probe between TP6 and TP5 for Vds measurement.

- Connect external inductor between CON1 and CON3. Use current probe to measure inductor current IL.

- 4. Set up and check PWM gate signal:

- a. Turn-on 12VDC power.

- b. Check the 2 LEDs on the daughter board. They should be turned on indicating the isolated 9V is present.

- c. Set up signal generator to create the waveforms as shown in Figure 13. Use equation  $I_{SW} = (V_{DS}*T_{ON1}) / L$  to calculate the pulse width of the first pulse and ensure the  $I_{SW}$  max is  $\leq 30A$  at 400VDC.

- d. Set the operation mode to either single trigger or Burst mode with repetition period of 100ms.

- e. Turn on the PWM output and check on the oscilloscope to make sure the VGL waveform is present and matches the PWM input.

### 5. Power-on:

a. Turn on the output of the HV supply. Start with low voltage and slowly ramp the voltage up until it reaches 400VDC. During the ramping period closely observe the voltage and current waveforms on the oscilloscope.

### 6. Power-off:

a. After the test is complete, slowly ramp down the HV supply voltage to 0V and turn off the output. Then turn off the 12V bias supply and signal generator output.

Figure 15 Double pulse test setup example (GS66508B-EVBDB1)

## 050V Gait E HEIMT Evaluation board reclinical Manad

## Test results – GS66508B-EVBDB1

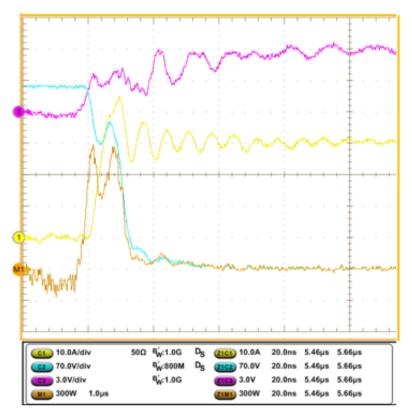

Double Pulse test (VDS=400V, IMAX = 30A, L=120uH, RG(ON)= $20\Omega$ , RG(OFF)= $20\Omega$ )

Figure 16 - 400V/30A double pulse test waveform

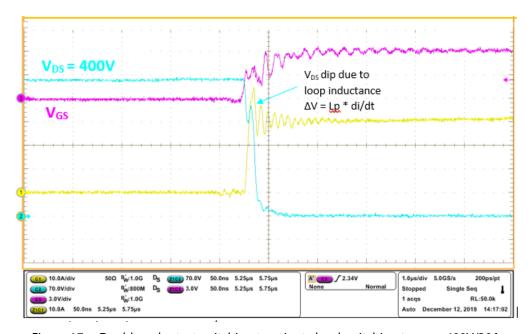

Figure 16 shows the hard switching on waveforms at 400V/30A. A Vds dip can be seen due to the rising drain current (di/dt in the power loop  $\Delta V$ =Lpxdi/dt, where Lp is the total power loop inductance). After the drain current reaches the inductor current, the Vds starts to fall. The Vgs undershoot spike is caused by the miller feedback via Cgd under negative dv/dt.

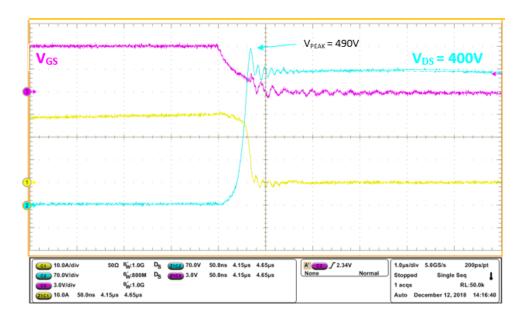

Due to the low gate charge and small  $R_{G(OFF)}$ , GaN E-HEMT gate has limited control on the turn-off dv/dt. Instead the Vds rise time is determined by how fast the turn-off current charges switching node capacitance (Coss).

The low Coss of GaN E-HEMT and low parasitic inductance of GaNP® package together with optimized PCB alyout, enables a fast and clean turn-off Vds waveform with only 50V the turn-off Vds overshoot at dv/dt > 100V/ns. The measured rise time is 3.9ns at 400V and 30A hard turn-off  $\circ$

Figure 17 - Double pulse test switching transient - hard switching turn-on 400V/30A

Figure 18 - Double pulse test switching transient - hard switching turn-off 400V/30A

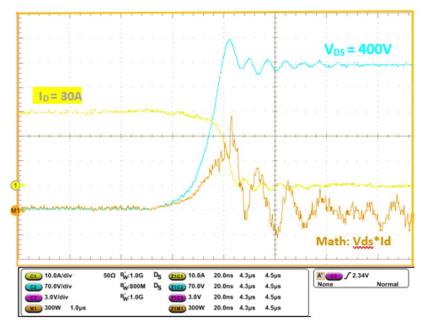

### Switching Loss energy (Eon/Eoff) measurement

A T&M search coaxial current shunt (SDN-414-10,  $0.1\Omega$ ) is installed for switching loss measurement as shown below.

Figure 1917 - Eon/Eoff measurement probe connection with current shunt

Figure 2018 - Eon/Eoff measurement and test bench setup

The switching energy can be calculated from the measured switching waveform Psw = Vds\*Id. The integral of the Psw during switching period is the measured switching loss. The channel deskewing is critical for measurement accurary. It is recommended to manually deskew Id against Vds as shown in Figure 20. The drain current spike is caused by charging the high side switch Coss (Qoss loss).

Figure 21 - Turn-on switching loss measurement (Eon=106uJ, 400V/30A)

Figure 19 - Turn-off switching loss measurement (Eoff=76 uJ, 400V/30A)

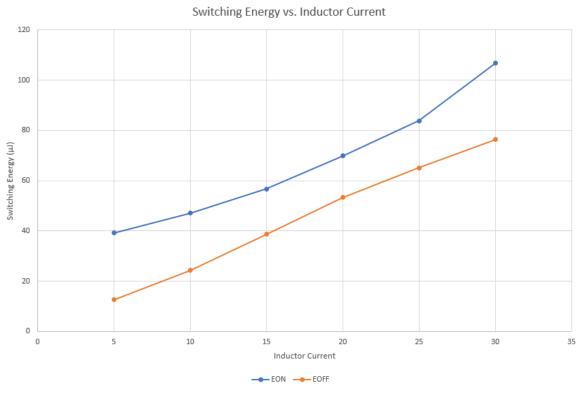

The switching loss measurements with drain current from 0 to 30A can be found in Figure 22. The turnon loss dominates the overall hard switching loss. Eon at 0A is the Qoss loss caused by the Coss at high side switch.

The turn-off loss remain almost constant from 0A up to 20A about 8uJ. the measured Eoff matches well with the Eoss @400V, which indicates that turn-off energy is dominated by Eoss, the energy required to charge Coss from 0V to bus voltage. This energy is not part of loss at turn-off, but actually part of turn-on loss at next hard switching turn-on period. This means that with the fast turn-off speed the GaN E-HEMT can achieve near zero turn-off switching loss.

Figure 20 - GS66508B Switching Loss Measurement (VDS = 400V, TJ=25°C)

## Appendix A - GS66508B-EVBDB1 Circuit schematic

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

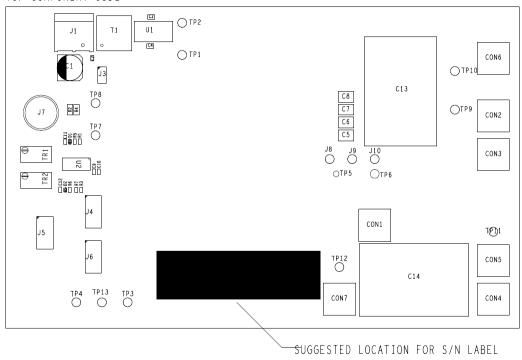

## **Assembly Drawing**

### TOP SIDE COMPONENTS

### **BOTTOM SIDE COMPONENTS**

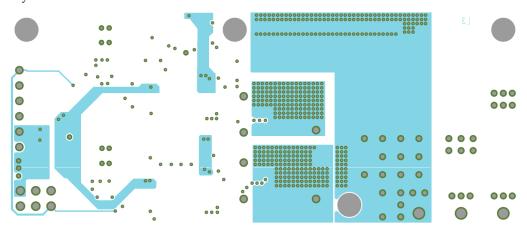

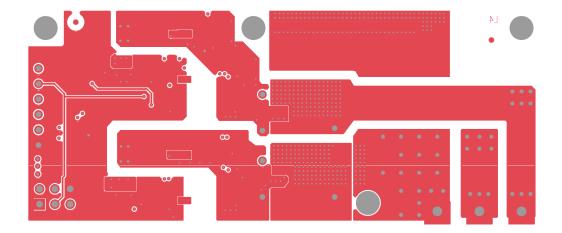

## **PCB** layout

## Top and Silk Layer

## Top

## Layer 2

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

#### **Bottom**

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

Bill of Materials GS66508B-EVBDB1

ADuM4121\_HBD\_BOM For GS66508B-EVBDB1

| Qty | DESCRIPTION                                                                               | VALUE                   | JEDEC_TYPE          | LOCATION           | Manufacturer              | Manufacturer Part Number |

|-----|-------------------------------------------------------------------------------------------|-------------------------|---------------------|--------------------|---------------------------|--------------------------|

| 6   | CAP CER X7R                                                                               | 4.7UF                   | C0805H53            | C1-C3,C14-C16      | TAIYO YUDEN               | TMK212AB7475KG-T         |

| 8   | CAP CER X7R, HIGH VOLTAGE                                                                 | 0.1uF                   | C1812H71            | C4-C11             | KEMET CORPORATION         | C1812V104KDRACTU         |

| 4   | CAP CER 0603 X7R                                                                          | 0.1uF                   | C0603               | C12,C13,C17,C18    | KEMET CORPORATION         | C0603C104K3RACTU         |

| 2   | CAP CER X5R                                                                               | 10uF                    | C0805-2             | C19,C20            | TAIYO YUDEN               | LMK212BJ106KD-T          |

| 2   | CAP CER X7R 0603                                                                          | 0.47uF                  | C0603               | C21,C22            | MURATA MANUFACTURING      | GRM188R71E474KA12D       |

| 3   | CONN-PCB 1POS BRD EDGE RIVET MOUNT FOR<br>62MILS BRD, 40MILS PIN SIZE, 200MILS PIN LENGTH | 3620-2-32-15-00-00-08-0 | CNMILLMAX3620       | CON1-CON3          | MILL-MAX                  | 3620-2-32-15-00-00-08-0  |

| 11  | RES FILM SMD 0603                                                                         | 0                       | R0603               | R7,FB1-FB3,R17-R22 | MULTICOMP                 | MC0603WG00000T5E-TC      |

| 1   | CONN-PCB BERG HDR DOUBLE STR MALE 6P                                                      | TSW-103-08-G-D-RA       | CNSAMTEC2X3H330LD36 | J1                 | SAMTEC                    | TSW-103-08-G-D-RA        |

| 1   | CONN-PCB BERG HDR ST FEM 6P                                                               | SSW-106-01-G-S          | CNBERGF1X6H330LD31  | J2                 | SAMTEC                    | SSW-106-01-G-S           |

| 1   | CONN-PCB JUMPER MICRO-MINI 6.9MM                                                          | 5102                    | CNKEYSTONE5102      | JP1                | KEYSTONE                  | 5102                     |

| 2   | LED GREEN CLEAR                                                                           | QTLP600C4TR             | LED0603             | LED1,LED2          | FAIRCHILD SEMICONDUCTOR   | QTLP600C4TR              |

| 2   | MOD DC-DC CONVERTER 5VIN 9VOUT 1W                                                         | PES1-S5-S9-M            | MPES1-SX-SX-M       | PS1,PS2            | CULINC                    | PES1-S5-S9-M             |

| 2   | TRAN GANFET BOTTOM-SIDE COOLED 650V E-<br>MODE, PRELIM                                    | GS66508B                | DIE4_8_38X6_98      | Q1,Q2              | GANSYSTEMS                | GS66508B                 |

| 7   | RES FILM SMD 0603                                                                         | 3.3K                    | R0603               | R2-R4,R8-R10,R13   | MULTICOMP                 | MC0.063W06031%3K3.       |

| 2   | RES PRECISION THICK FILM CHIP R0603                                                       | 20                      | R0603               | R6, R12            | ROHM                      | ESR03EZPJ200             |

| 4   | RES PRECISION THICK FILM CHIP R0603                                                       | 10                      | R0603               | R5,R11,R15,R16     | PANASONIC                 | ERJ-3EKF10R0V            |

| 2   | IC MICROPOWER LOW-NOISE ULTRA LOW DROPOUT REGULATOR                                       | LP2985IM5-6.1/NOPB      | SOT23-5L-2          | U1,U3              | TEXAS INSTRUMENTS         | LP2985IM5-6.1/NOPB       |

| 2   | IC-ADI HV ISOLATED GATE DRIVER WITH MILLER CLAMP PRELIM                                   | ADUM4121ARZ             | SO8WB_A             | U2,U4              | ADI                       | ADUM4121ARZ              |

| 1   | IC-ADI LDO REGULATOR 3.3V OUT                                                             | ADP3309ARTZ-3.3         | SOT23-5L-2          | U5                 | ADI                       | ADP3309ARTZ-3.3          |

| 1   | RES FILM SMD 0603                                                                         | 0                       | R0603               | R1, R14            | MULTICOMP                 | MC0603WG00000T5E-TC      |

| 1   | DIODE TVS UNIDIRECTIONAL                                                                  | SMAJ7.5A                | DO214AC_A           | D1                 | LITTELFUSE, INC.          | SMAJ7.5A                 |

| 6   | CONN-PCB TST PNT BLK                                                                      | 5001                    | CNKEY5001TP         | TP1-TP6            | KEYSTONE ELECTRONICS CORP | 5001                     |

| 1   | heatsink, 35x35mmx25.4mm, black anodized                                                  |                         |                     |                    | Cool Innovation           | 3-141410UBLAN            |

| 1   | Thermal sheet cut to 35x35mm square                                                       |                         |                     |                    | BOND PLY                  | BOND PLY 100             |

## Appendix B - GS665MB-EVB

### **Circuit schematics**

## **Assembly drawing**

## **Assembly Top**

TOP COMPONENT SIDE

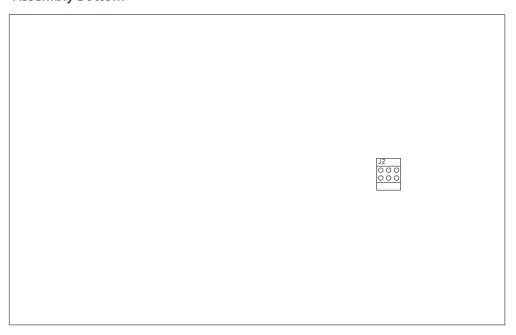

## **Assembly Bottom**

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

## **Bill of Materials**

| GAN SYSTEMS 650V GAN UNIVERSAL MOTHER BOATRD |            |  |  |  |

|----------------------------------------------|------------|--|--|--|

| BOARD P/N:                                   | GS665EVBMB |  |  |  |

| Revision                                     | B1         |  |  |  |

| Last Undate                                  | 6/30/2016  |  |  |  |

| Last Update      | 6/30/2016                           |                                              |                        |                 |                         |                                                        |

|------------------|-------------------------------------|----------------------------------------------|------------------------|-----------------|-------------------------|--------------------------------------------------------|

| Quantity         | Reference                           | Description                                  | Value                  | Manufacturer    | Part number             | Assembly Note                                          |

| Quantity         | 1 PCB                               | PCB bare 2-layer 2oz Cu.                     | Value                  | Wallulacturei   | rait ilullipei          | Assembly Note                                          |

|                  | CON1,CON2,CON3,CON4,C               | PCB bare 2-layer 202 Cu.                     |                        |                 |                         |                                                        |

| 1                | 7 ON5,CON6,CON7                     | TERMINAL SCREW VERTICAL PC MNT               | CON-10-32-SCRWMNT      | KEYSTONE        | 8191                    | DO NOT INSTALL                                         |

| 2                | 1 C1                                | CAP ALUM 220UF 20% 25V SMD                   | 220uF 25V              | Panasonic       | EEE-FK1E221P            |                                                        |

| 3                | 1 C2,C10                            | GENERIC 1UF/25V, 10% X7R SMD 0603            | 1uF                    | TAIYO YUDEN     | TMK107B7105KA-T         |                                                        |

| 4                | 2 C3,C4                             | GENERIC 10UF/25V, 10% SMD 0805               | 10uF                   | TAIYO YUDEN     | TMK212BBJ106KG-T        |                                                        |

| 5                | 4 C5,C6,C7,C8                       | GENERIC 0.1uF/1000V, SMD 1812                | 0.1uF 1kV              | KEMET           | C1812C104KDRAC7800      |                                                        |

| 6                | 1 C9                                | GENERIC 0.1UF/25V, 10% X7R SMD 0603          | 0.1uF                  | TAIYO YUDEN     | TMJ107BB7104KAHT        |                                                        |

| 7                | 2 C11,C12                           | GENERIC 100PF/25V 5% NP0 SMD 0603            | 100pF                  | KEMET           | C0603C101J3GACTU        |                                                        |

| 8                | 1 C13, <del>C14</del>               | CAP FILM 10UF/600VDC 5%, 27.5MM LEAD SPACING | 10uF 700V              | KEMET           | C4AEHBU5100A11J         | DO NOT INSTALL C14                                     |

| 9                | 2 D1,D2                             | DIODE SCHOTTKY 20V 500MA SOD523              | PMEG2005EB             | NXP             | PMEG2005EB,115          |                                                        |

| 10               | 1 J1                                | TERM BLOCK HDR 2POS R/A 5.08MM               | CON-TERM-BLK-2POS-RA   | TE CONNECTIVITY | 796638-2                |                                                        |

| 11               | 1 J1-PLUG                           | TERM BLOCK BLUG 2POS 5.08MM                  |                        | TE CONNECTIVITY | 796634-2                |                                                        |

| 12               | 1 J2                                | CONN RCPT 6POS .100 DBL STR PCB              | CON-RCPT-2X3-BOT       | HARWIN          | M20-7850342             | MOUNT FROM BOTTOM SIDE                                 |

| 13               | 1 J3                                |                                              | CON-2POS               |                 |                         | CONNECTOR FOR 12V FAN, DO NOT INSTALL                  |

| 14               | 2 J4,J6                             | CONN HEADER 8POS DUAL VERT PCB               | CON-JMP-4POS           | HARWIN          | M20-9980445             |                                                        |

| 15               | 1 J5                                | CONN 8-POS, DUAL ROW 2.54MM                  | CON-HDR-4X2            | AMPHENOL        | 75869-132LF             |                                                        |

| 16               | 1 J7                                | CONN BNC JACK STR 50 OHM PCB                 | 112538                 | AMPHENOL        | 112538                  |                                                        |

| 47               | 0 10 10 140                         | CONNECTED TO DIA COO CACIL CZEII             | CON DODT ED CEMMIT     | NAII I NAAN     | 0040 0 45 45 04 07 40 0 | MATING SOCKET FOR MILLMAX<br>EDGE MNT PIN              |

| 17               | 3 J8,J9,J10                         | CONN RECEPT PIN .032046" .075"               | CON-RCPT-EDGEMNT       | MILLMAX         | 0312-0-15-15-34-27-10-0 | EDGE MINT FIN                                          |

| 18               | 3 R1,R3,R7                          | generic 1% smd 0603                          | 49R9                   | VISHAYDALE      | CRCW060349R9FKEA        |                                                        |

| 19               | 2 R2,R4                             | generic 1% smd 1206                          | 100R                   | VIOLIAN/DALE    | 00014100004140051454    | DO NOT INSTALL                                         |

| 20               | 2 R5,R6<br>TP1,TP2,TP3,TP4,TP7,TP8, | generic 1% snd 0603                          | 1K00                   | VISHAYDALE      | CRCW06031K00FKEA        |                                                        |

| 21               | 11 TP9,TP10,TP11,TP12,TP13          | TEST POINT PCB                               | TP-KEYSTONE-5010       | KEYSTONE        | 5010                    |                                                        |

| 22               | 2 TR1,TR2                           |                                              | 2K                     | RECOM           | CMC-08                  | DO NOT INSTALL                                         |

| 23               | 1 T1                                | COMM MODE CHOKE 5.2A T/H                     | CMC-08                 |                 |                         |                                                        |

| 24               | 1 U1                                | IC REG LDO 5V 1A DPAK                        | MC7805                 | ON SEMI         | MC7805BDTRKG            |                                                        |

| 25               | 1 U2                                | 1 IC GATE NAND 4CH 2-INP 14-SOIC             | 74VHC132               | FAIRCHILD       | 74VHC132MX              |                                                        |

| Off the board co | mponents:                           |                                              |                        |                 |                         |                                                        |

| 26               | 6 M1,M2,M3,M4,M5,M6                 | PCB STANDOFF NYLON STACKABLE 4.75M           | MECH-STDOFF-KEYSTONE-8 | KEYSTONE        | 8833                    | PCB SPACER, INSTALL FROM BOTTOM SIDE                   |

| 27               | 1 FAN                               | FAN AXIAL 38X20MM 12VDC WIRE                 |                        | SUNON FANS      | PMD1238PKB1-A.(2).GN    | SUPPLY LOOSE, DO NOT INSTALL ON THE ASSEMBLY           |

| 28               | 2 JUMPER                            | JUMPER SHUNT GENERIC                         |                        | TE CONNECTIVITY | 382811-8                | INSTALL ON J4 "INT" POSITION AND J6 "INT_INV" POSITION |

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

#### **Evaluation Board/kit Important Notice**

GaN Systems Inc. (GaN Systems) provides the enclosed product(s) under the following AS IS conditions:

This evaluation board/kit being sold or provided by GaN Systems is intended for use for ENGINEERING DEVELOPMENT, DEMONSTRATION, and OR EVALUATION PURPOSES ONLY and is not considered by GaN Systems to be a finished end-product fit for general consumer use. As such, the goods being sold or provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives, or other related regulations.

If this evaluation board/kit does not meet the specifications indicated in the Technical Manual, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies GaN Systems from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

No License is granted under any patent right or other intellectual property right of GaN Systems whatsoever. GaN Systems assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.

GaN Systems currently services a variety of customers for products around the world, and therefore this transaction **is not exclusive**.

Please read the Technical Manual and, specifically, the Warnings and Restrictions notice in the Technical Manual prior to handling the product. Persons handling the product(s) must have electronics training and observe good engineering practice standards.

This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a GaN Systems' application engineer.

# GS66508B-EVBDB1 650V GaN E-HEMT Evaluation Board Technical Manual

In Canada:

GaN Systems Inc. 1145 Innovation Drive Suite 101 Ottawa, Ontario, Canada K2K 3G8 T+1 613-686-1996 In Europe:

GaN Systems Ltd., German Branch Terminalstrasse Mitte 18, 85356 München, Germany T+49 (0) 8165 9822 7260 In the United States:

GaN Systems Corp. 2723 South State Street, Suite 150, Ann Arbor, MI. USA 48104 T+1 248-609-7643

#### www.gansystems.com

Important Notice – Unless expressly approved in writing by an authorized representative of GaN Systems, GaN Systems components are not designed, authorized or warranted for use in lifesaving, life sustaining, military, aircraft, or space applications, nor in products or systems where failure or malfunction may result in personal injury, death, or property or environmental damage. The information given in this document shall not in any event be regarded as a guarantee of performance. GaN Systems hereby disclaims any or all warranties and liabilities of any kind, including but not limited to warranties of non-infringement of intellectual property rights. All other brand and product names are trademarks or registered trademarks of their respective owners. Information provided herein is intended as a guide only and is subject to change without notice. The information contained herein or any use of such information does not grant, explicitly, or implicitly, to any party any patent rights, licenses, or any other intellectual property rights. General Sales and Terms Conditions apply.

© 2009-2020 GaN Systems Inc. All rights reserved.